Paper Title Number 2

Published in Journal 1, 2010

This paper is about the number 2. The number 3 is left for future work.

Recommended citation: Your Name, You. (2010). "Paper Title Number 2." Journal 1. 1(2).

Download Paper | Download Slides

A list of all the posts and pages found on the site. For you robots out there is an XML version available for digesting as well.

Published in Journal 1, 2010

This paper is about the number 2. The number 3 is left for future work.

Recommended citation: Your Name, You. (2010). "Paper Title Number 2." Journal 1. 1(2).

Download Paper | Download Slides

Published in Journal 1, 2015

This paper is about the number 3. The number 4 is left for future work.

Recommended citation: Your Name, You. (2015). "Paper Title Number 3." Journal 1. 1(3).

Download Paper | Download Slides

Published in Conference, 2022

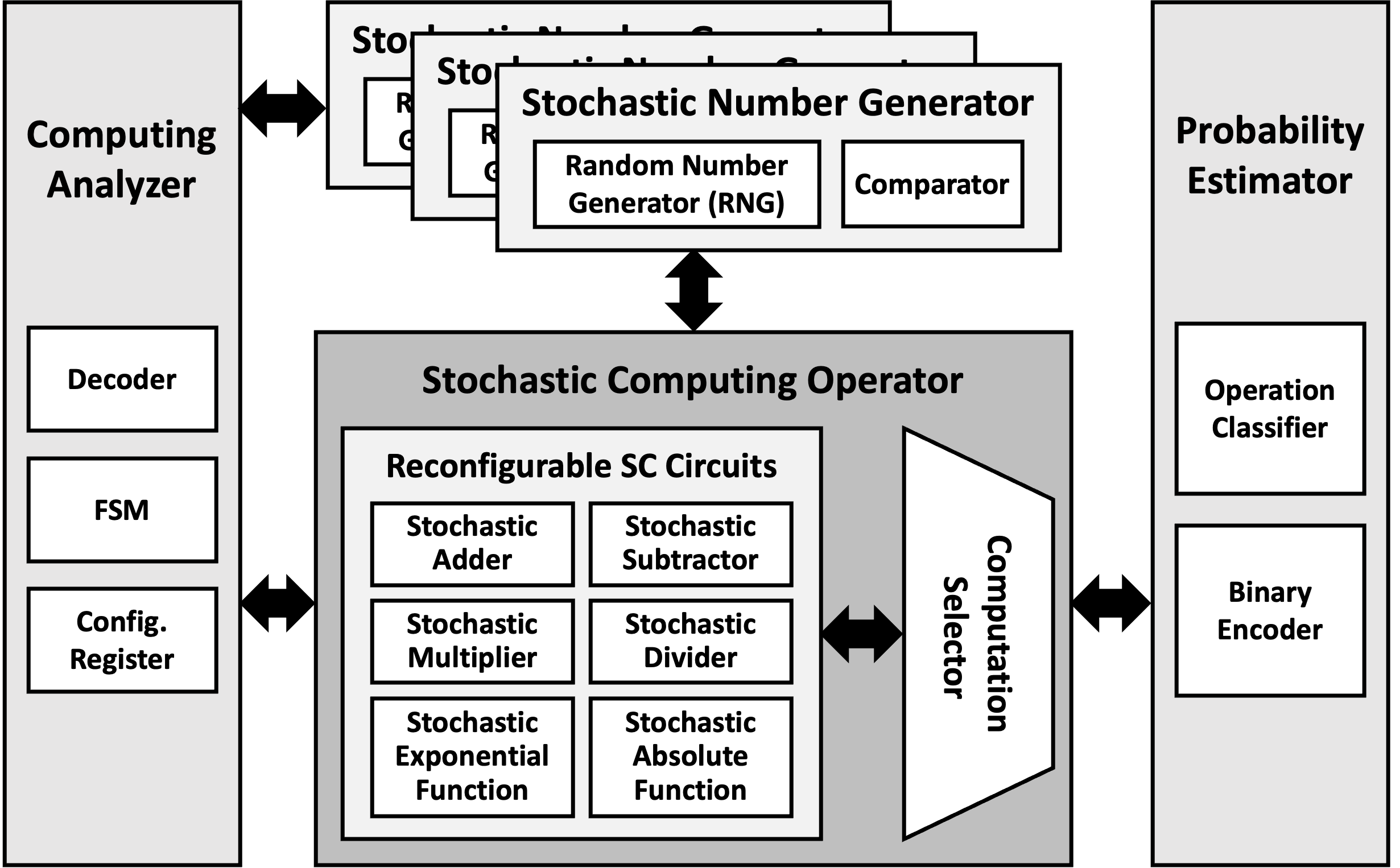

Recommended citation: J. Kim, Y. R. Jeong, K. Cho, W. S. Jeong and S. E. Lee, "Reconfigurable Stochastic Computing Architecture for Computationally Intensive Applications," 2022 19th International SoC Design Conference (ISOCC), Gangneung-si, Korea, Republic of, 2022, pp. 61-62.

Download Paper | Download Slides

Published in Journal 1, 2021

Published in Poster, 2023

Published in Journal 1, 2023

Published in GitHub Journal of Bugs, 2024

This paper is about fixing template issue #693.

Recommended citation: Your Name, You. (2024). "Paper Title Number 3." GitHub Journal of Bugs. 1(3).

Download Paper

Published:

This is a description of your talk, which is a markdown file that can be all markdown-ified like any other post. Yay markdown!

Published:

This is a description of your conference proceedings talk, note the different field in type. You can put anything in this field.

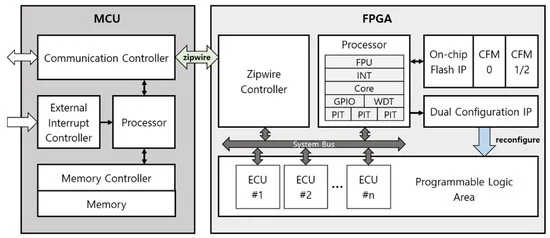

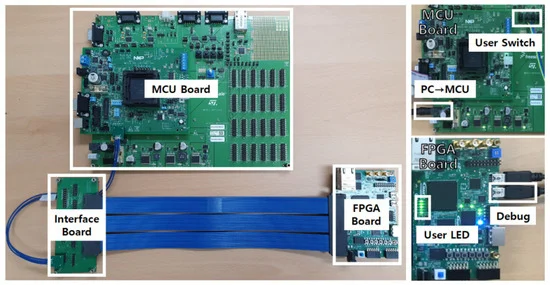

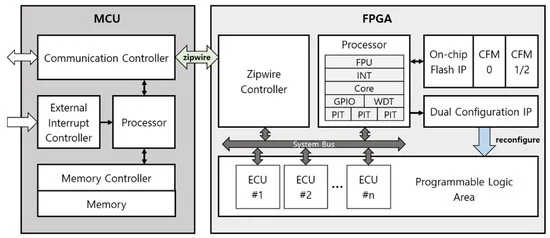

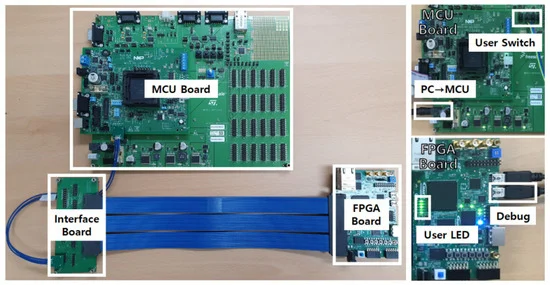

Published in Micromachines, 2021

Recommended citation: Cho, K.; Kim, J.; Choi, D.Y.; Yoon, Y.H.; Oh, J.H.; Lee, S.E. An FPGA-Based ECU for Remote Reconfiguration in Automotive Systems. Micromachines 2021, 12, 1309.

Download Paper

Published in 2022 IEEE International Conference on Consumer Electronics (ICCE), 2022

Recommended citation: K. Cho, H. W. Oh, J. Kim, Y. W. Jeong and S. E. Lee, "A Local Interconnect Network Controller for Resource-Constrained Automotive Devices," 2022 IEEE International Conference on Consumer Electronics (ICCE), Las Vegas, NV, USA, 2022, pp. 1-3.

Download Paper

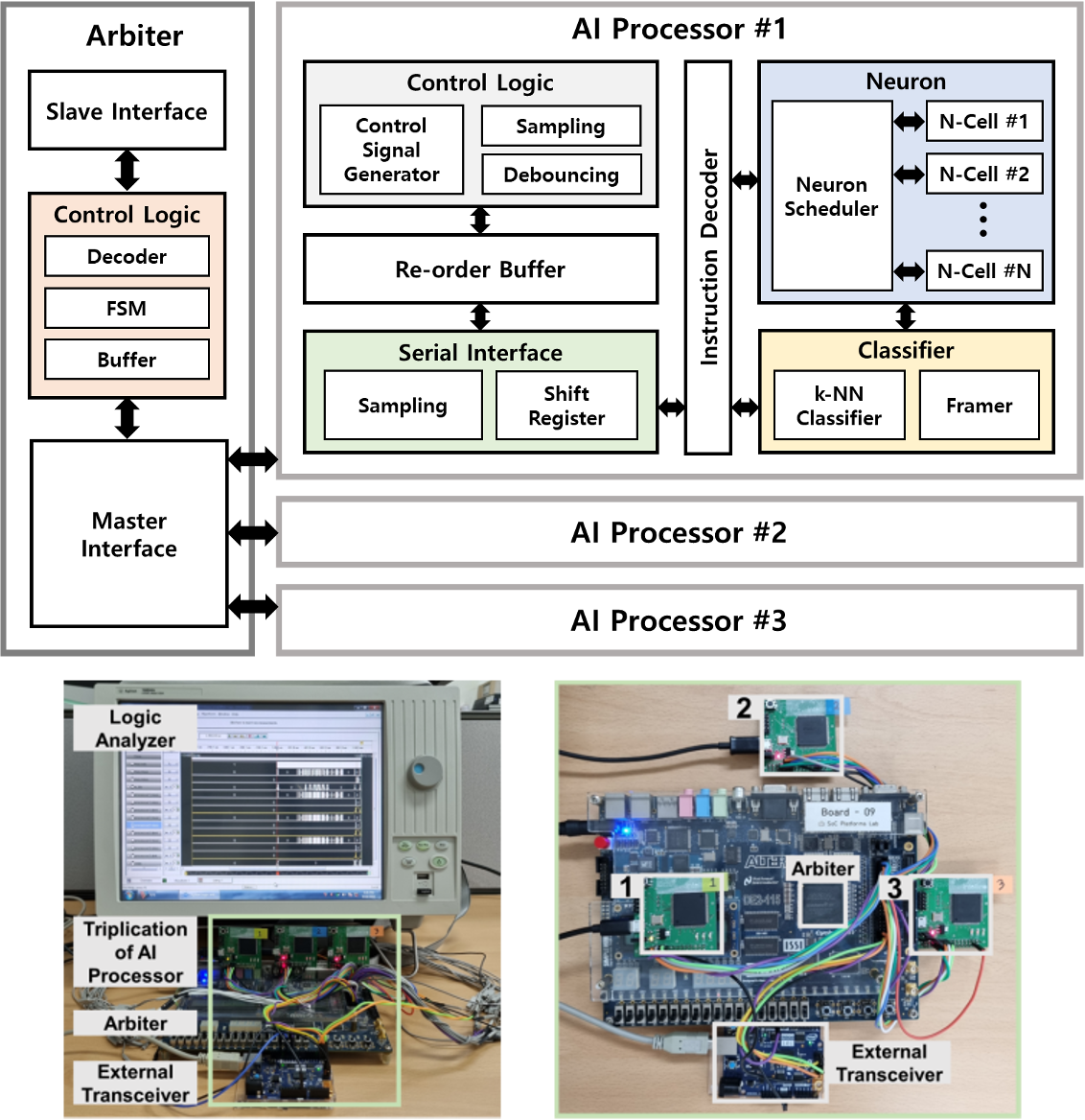

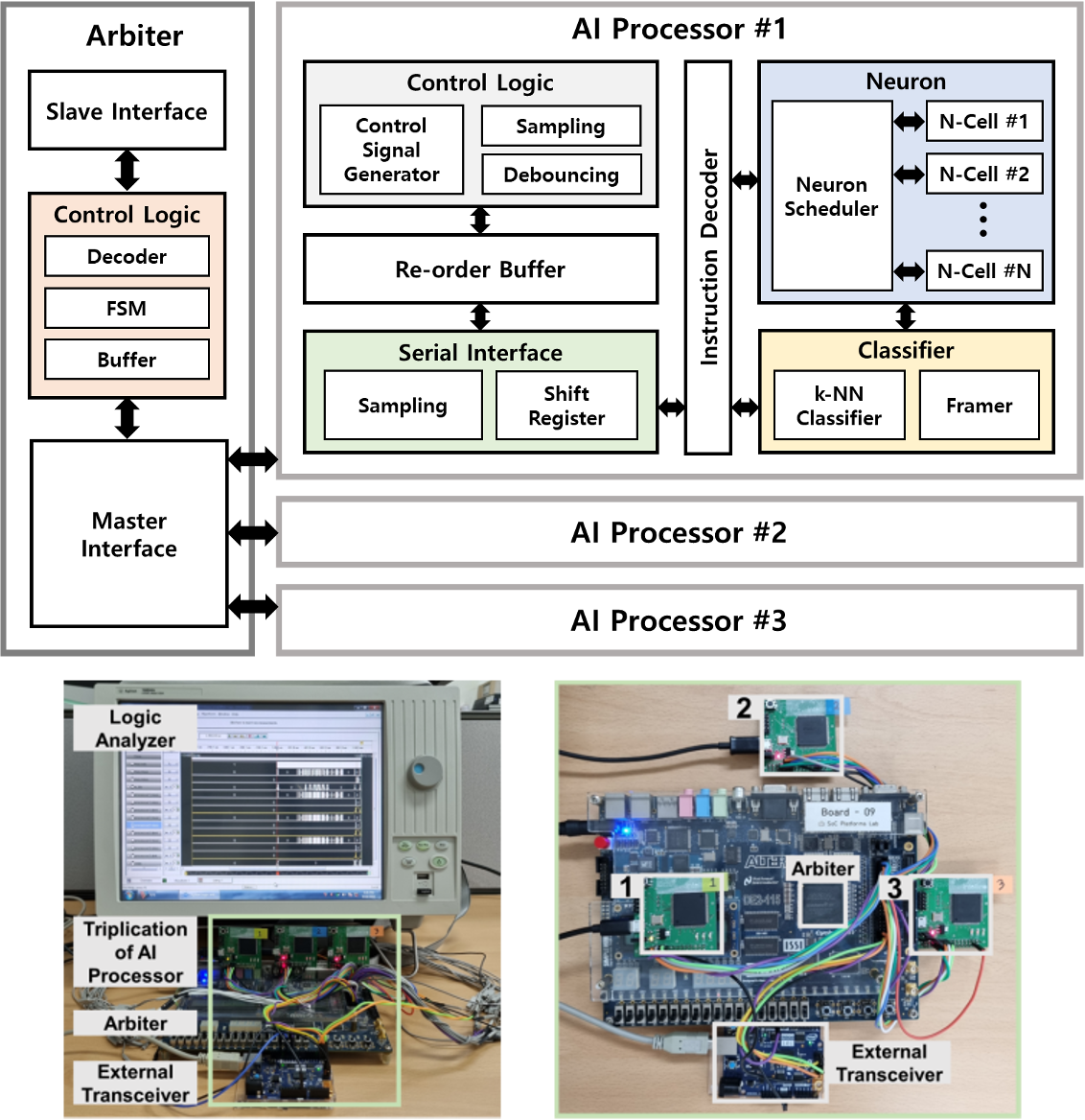

Published in International Conference on Parallel Architectures and Compilation Techniques(PACT 2022), 2022

Recommended citation: Jeongeun Kim, Youngwoo Jeong, Suyeon Jang, and Seung Eun Lee. 2023. An Architecture for Resilient Federated Learning through Parallel Recognition. In Proceedings of the International Conference on Parallel Architectures and Compilation Techniques (PACT 22). Association for Computing Machinery, New York, NY, USA, 546–547.

Download Paper

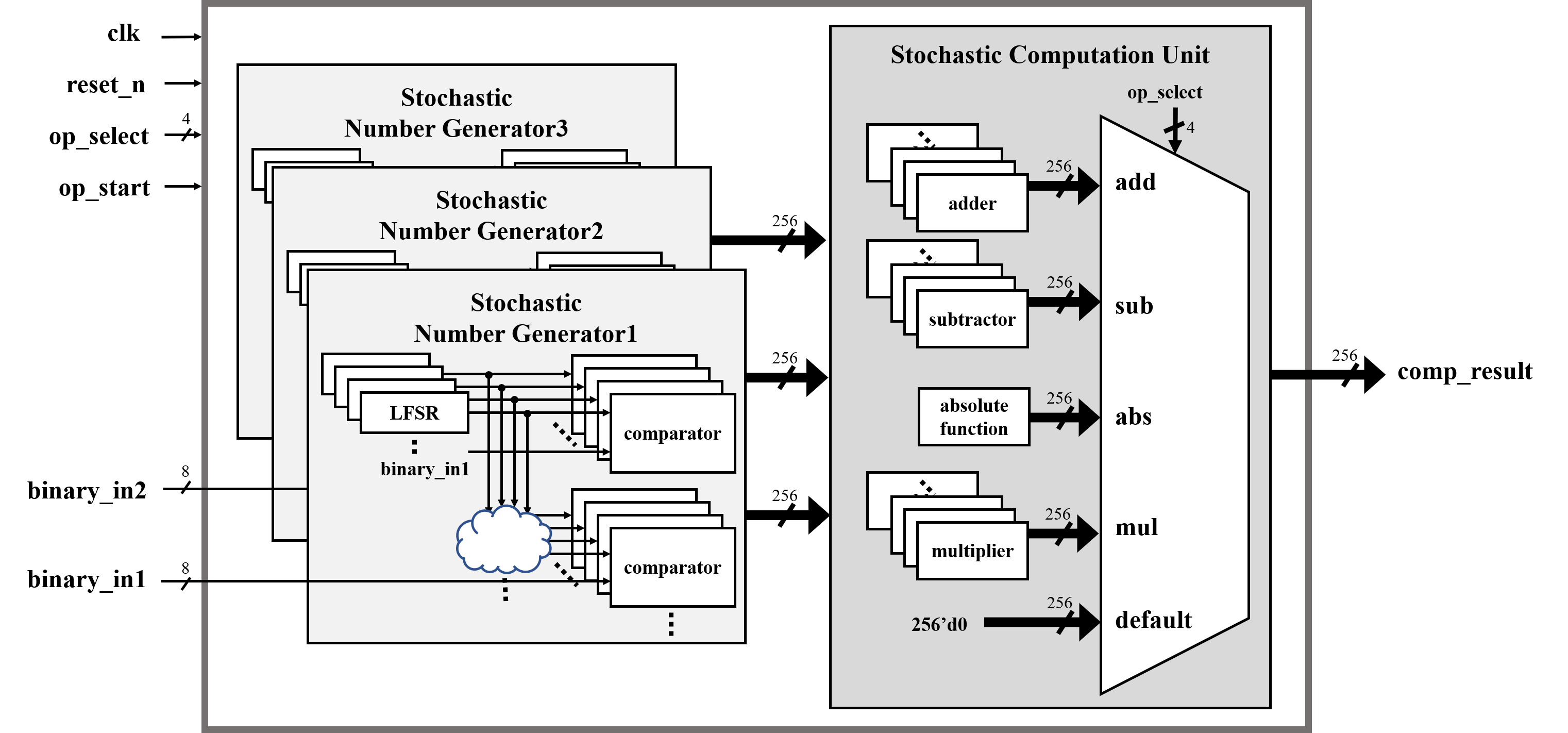

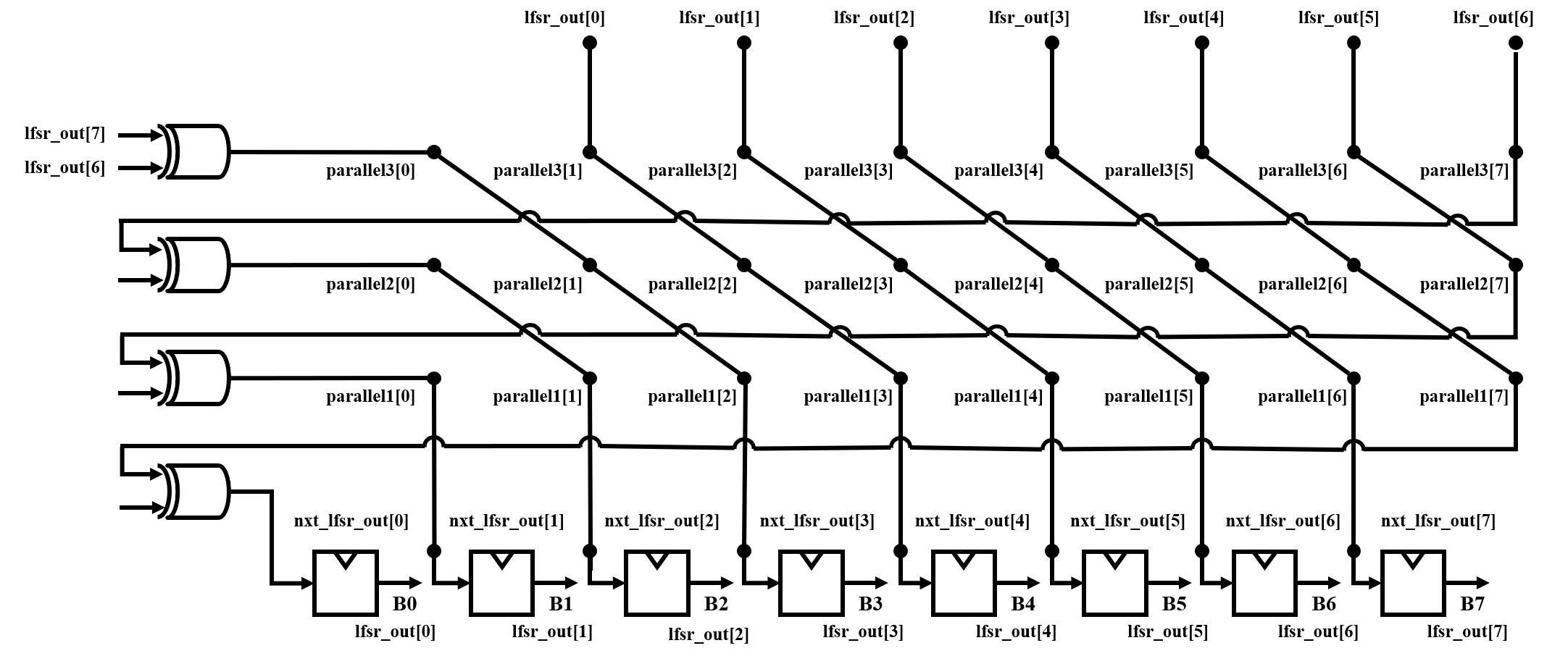

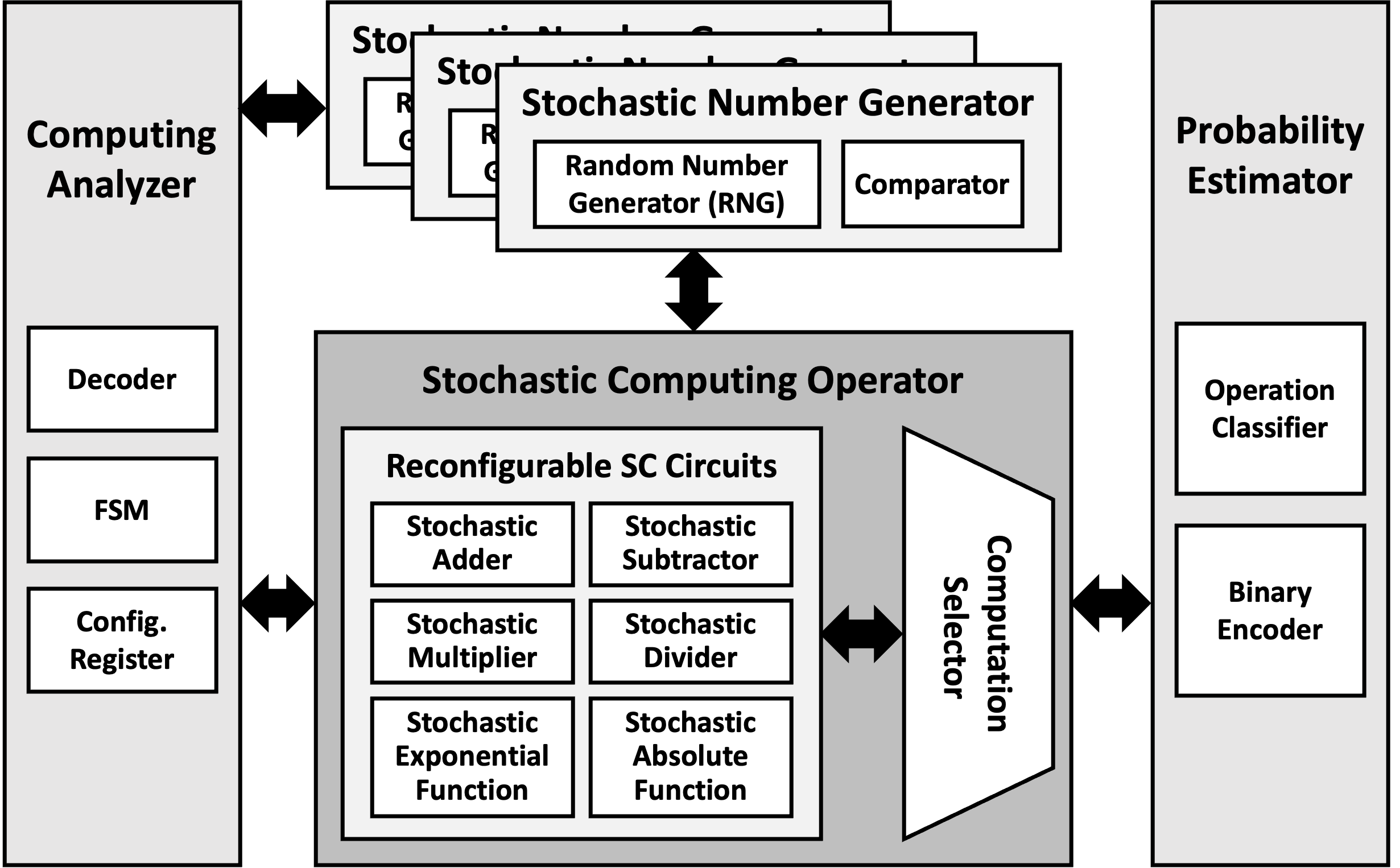

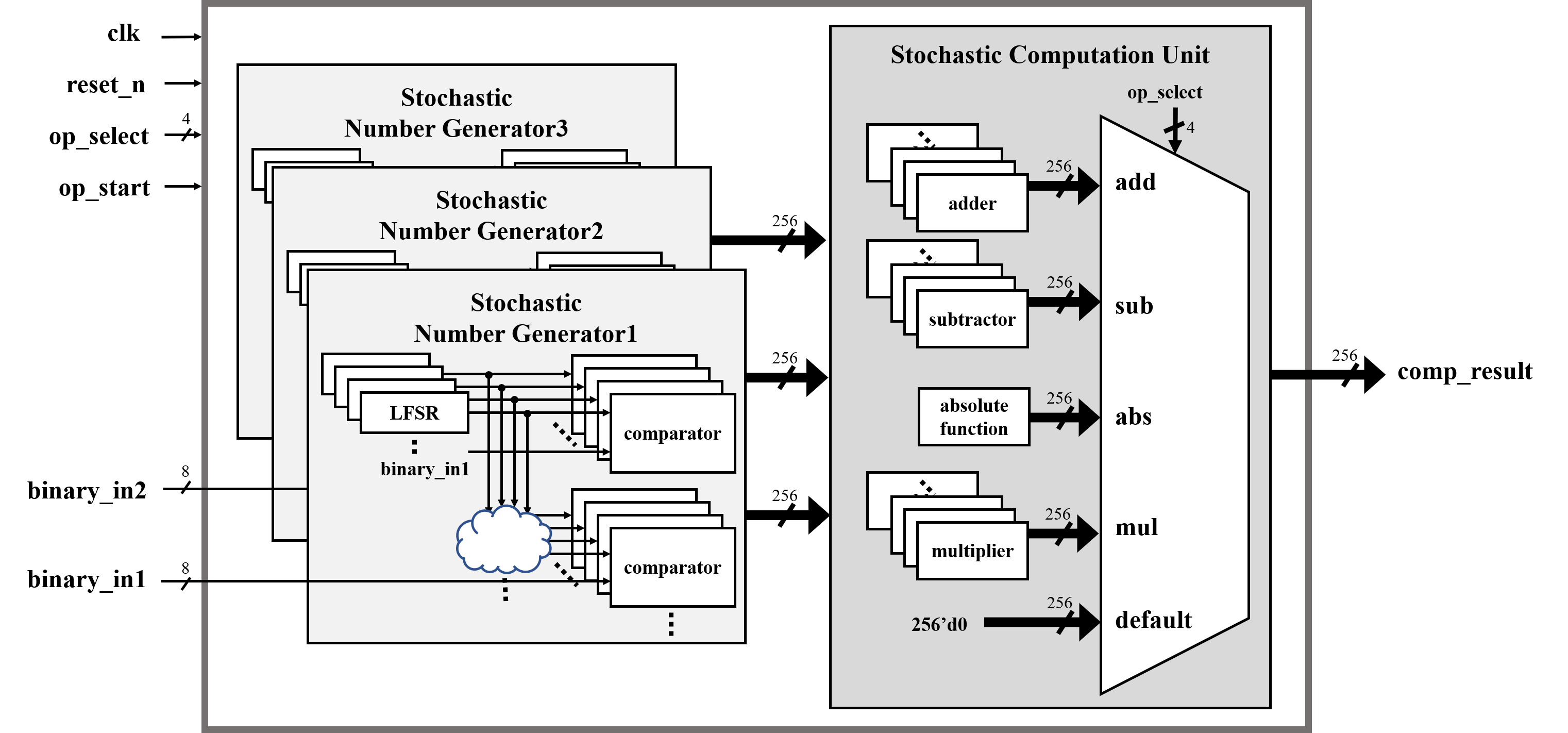

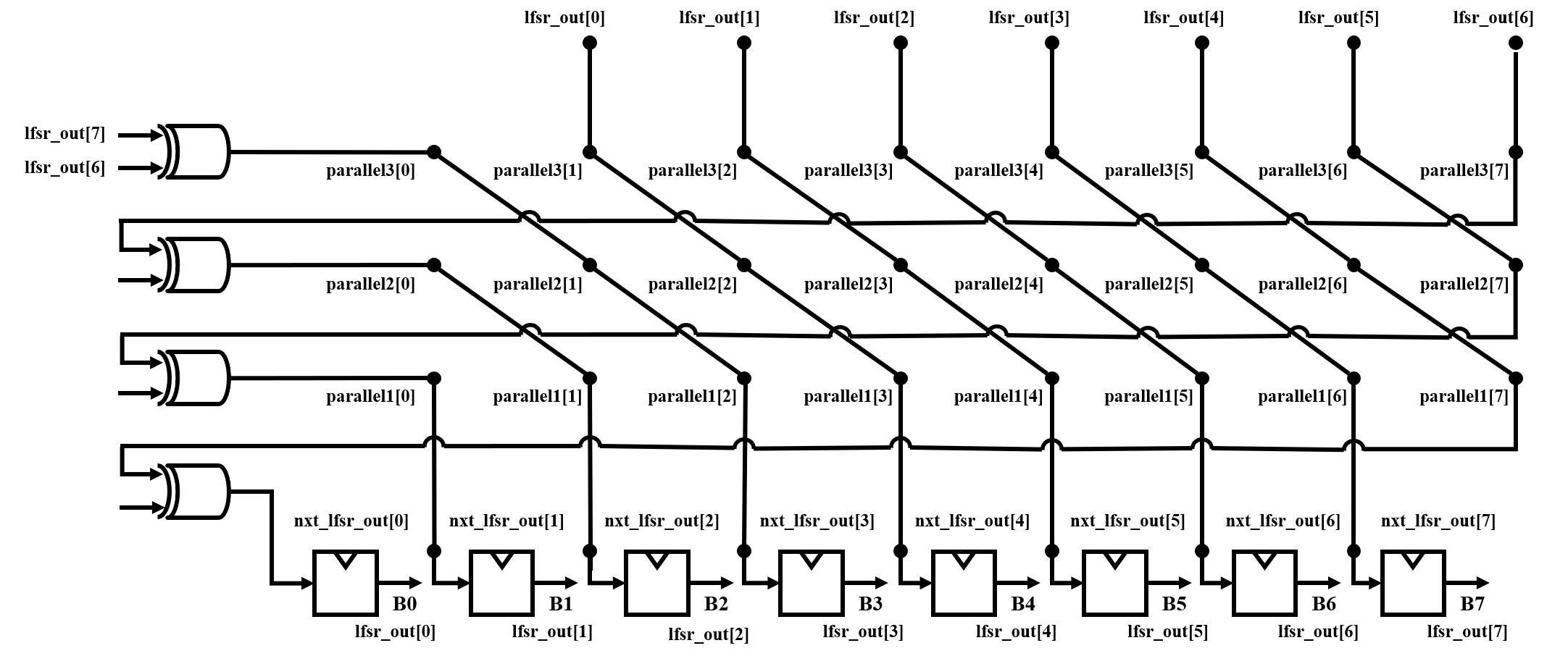

Published in 19th International SoC Design Conference (ISOCC 2022), 2022

Recommended citation: J. Kim, Y. R. Jeong, K. Cho, W. S. Jeong and S. E. Lee, "Reconfigurable Stochastic Computing Architecture for Computationally Intensive Applications," 2022 19th International SoC Design Conference (ISOCC), Gangneung-si, Korea, Republic of, 2022, pp. 61-62.

Download Paper

Published in Electronics, 2023

Recommended citation: Kim, J.; Jeong, W.S.; Jeong, Y.; Lee, S.E. Parallel Stochastic Computing Architecture for Computationally Intensive Applications. Electronics 2023, 12, 1749.

Download Paper

Undergraduate course, Seoultech, Department of Electronic Engineering, 2021

Term: Spring 2021

This course focuses on system design using computers, covering methods for addressing design requirements such as modeling and simulation. It emphasizes the use of computer-aided design (CAD) tools to solve these problems effectively.

Undergraduate course, Seoultech, Department of Electronic Engineering, 2021

Term: Fall 2021

This course builds upon the foundations of Digital Engineering and Introduction to Computer Programming, exploring the execution and operation of instructions within a computer, along with the associated logic and organization. The primary focus is on CPU architecture, covering:

Graduate course, Seoultech, Department of Electrical Engineering, 2021

Term: Fall 2021

Graduate course, USC, Department of Electrical and Computer Engineering, 2024

Term: Fall 2024

This course offers students the opportunity to apply their expertise in architecture and VLSI design to develop hardware for an application of their choice and complete a full chip design cycle within a 15-week timeline. The course culminates in students taping out their own chip using Intel’s advanced 16nm technology.